480A1 Total Pages: 2

Register No.: Name:

# SAINTGITS COLLEGE OF ENGINEERING (AUTONOMOUS)

(AFFILIATED TO APJ ABDUL KALAM TECHNOLOGICAL UNIVERSITY, THIRUVANANTHAPURAM)

# SECOND SEMESTER M.TECH DEGREE EXAMINATION (R,S), MAY 2024 VLSI AND EMBEDDED SYSTEMS

(2021 Scheme)

Course Code: 21VE204-E

Physical Design and Verification Course Name:

Max. Marks: 60 **Duration: 3 Hours**

#### PART A

## (Answer all questions. Each question carries 3 marks)

- 1. Explain the term synthesis in IC design.

- 2. Illustrate the significance of static timing analysis in physical design.

- List the various inputs for routing. 3.

- 4. Enumerate the different types of floor planning.

- Explain the significance of clock tree optimization in physical design. 5.

- Illustrate clock tree synthesis flow. 6.

- 7. Describe clock tree power consumption.

- Explain logical equivalence checking associated with physical verification. 8.

#### PART B

## (Answer one full question from each module, each question carries 6 marks)

#### MODULE I

9. Compare frontend and backend design of an IC. (6)

#### OR

10. Explain command flow of synthesis with an example.

(6)

#### **MODULE II**

Explain static timing analysis and timing violations with relevant 11. diagrams. Illustrate how one can determine the maximum frequency (6)of operation of a circuit.

#### OR

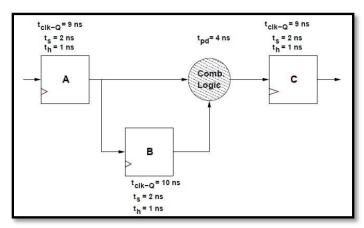

Analyze the following circuit and calculate the maximum clock 12. frequency that can be given to this circuit. (6)

#### **MODULE III**

13. Illustrate the following (a) Detailed Routing (b) Post route optimization (6)

#### OR

14. Demonstrate DRC and LVS in physical design of an IC.

## **MODULE IV**

15. Show the steps of floor planning in physical design with relevant diagrams. (6)

#### OR

16. Summarize the methods available to control and manage congestion during the placement process. (6)

# MODULE V

17. Explain clock tree optimization technique with an example.

# (6)

(6)

18. Illustrate skew balancing with the help of an example.

## (6)

(6)

#### **MODULE VI**

OR

19. Illustrate synchronous and cross clock balancing with relevant sketches.

### OR

20. Discuss the significance of TCL scripting in physical design with any two example script. (6)

\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*