**Total Pages: 3**

Reg No.:\_\_\_\_\_

Name:

# **APJ ABDUL KALAM TECHNOLOGICAL UNIVERSITY** FIFTH SEMESTER B.TECH DEGREE EXAMINATION, DECEMBER 2017

#### **Course Code: EC361**

## Course Name: DIGITAL SYSTEM DESIGN (EC, AE)

Max. Marks: 100

#### Duration: 3 Hours

Marks

#### PART A Answer any two full questions, each carries 15 marks.

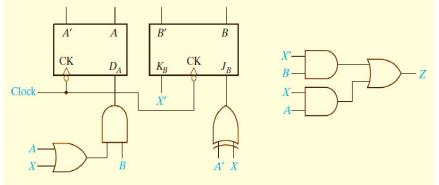

1 a) Analyse the following sequential network. Derive the next state and output (7.5) equations. Obtain its transition table and state table.

b) Analyse the asynchronous sequential network shown in figure, by forming the (7.5) excitation/transition table, state table, flow table, and flow diagram. The network operates in the fundamental mode with the restriction that only one input variable can change at a time.

- 2 a) Draw the ASM chart for a mod 8 binary up-down counter

- b) One type of clocked T-Flip-flop works as follows: The flip-flop has two inputs, T and P. The flip- flop will change state if T=1 when the clock(P) changes from 1 to 0. Under all other conditions, Q should remain constant. Assume that T and P do not change simultaneously. Obtain a minimal flow table.

- 3 a) Reduce the following State table using implication chart.

| Present<br>State | Next Sta $X = 0$ | ite<br>1 | Present<br>Output |

|------------------|------------------|----------|-------------------|

| а                | d                | с        | 0                 |

| b                | f                | h        | 0                 |

| с                | e                | d        | 1                 |

| d                | а                | e        | 0                 |

| е                | С                | a        | 1                 |

| f                | f                | Ь        | 1                 |

| g                | Ь                | h        | 0                 |

| ĥ                | с                | g        | 1                 |

(7.5)

(7.5)

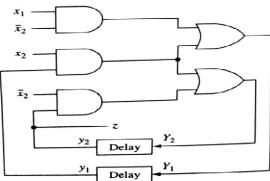

b) The reduced flow table shown below for a fundamental mode asynchronous (7.5) sequential network. Determine a state assignment involving a minimum number of variables that allows a realization free of critical races. Construct the corresponding transition table and obtain the minimal-sum expressions for realisations using feedback loops. Assume that both the inputs won't change simultaneously

|                                              | Next | state                                  | Output(z)                          |                                                                |                                                                            |                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                    |

|----------------------------------------------|------|----------------------------------------|------------------------------------|----------------------------------------------------------------|----------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|

| Input State(x <sub>1</sub> ,x <sub>2</sub> ) |      |                                        |                                    |                                                                | put St                                                                     | ate(x <sub>1</sub>                                                                                                                                                                                                                                                                                                                                                                         | ,x₂)                                                                                                               |

| 00                                           | 01   | 10                                     | 11                                 | 00                                                             | 01                                                                         | 10                                                                                                                                                                                                                                                                                                                                                                                         | 11                                                                                                                 |

| 1                                            | 1    | 4                                      | 1                                  | 0                                                              | 0                                                                          | -                                                                                                                                                                                                                                                                                                                                                                                          | 0                                                                                                                  |

| 2                                            | 1    | 3                                      | -                                  | 1                                                              | -                                                                          | -                                                                                                                                                                                                                                                                                                                                                                                          | -                                                                                                                  |

| 2                                            | 3    | 3                                      | 3                                  | -                                                              | 1                                                                          | 1                                                                                                                                                                                                                                                                                                                                                                                          | 1                                                                                                                  |

| 1                                            | -    | 4                                      | 3                                  | -                                                              | -                                                                          | 0                                                                                                                                                                                                                                                                                                                                                                                          | -                                                                                                                  |

|                                              | 1    | Input Sta<br>00 01<br>(1) (1)<br>(2) 1 | 00 01 10   ① ① ① 4   ② 1 3   2 ③ ③ | Input State(x1,x2)   00 01 10 11   ① ① 4 ①   ② 1 3 -   2 ③ ③ ③ | Input State(x1,x2) In   00 01 10 11 00   ① ① ① 1 0   ② 1 3 - 1   2 ③ ③ ③ - | Input State(x1,x2) Input St   00 01 10 11 00 01   ① ① ① ① ① ① ①   ① ① ① ① ① ① ①   ① ① ① ① ① ① ① ①   ① ① ① ① ① ① ② ② ① ② ② ① ① ② ② ① ③ ③ ③ ③ ○ ① ② ② ① ③ ③ ③ ○ ① ③ ③ ○ ○ ○ ○ ○ ○ ○ ○ ○ ○ ○ ○ ○ ○ ○ ○ ○ ○ ○ ○ ○ ○ ○ ○ ○ ○ ○ ○ ○ ○ ○ ○ ○ ○ ○ ○ ○ ○ <t< td=""><td>Input State(x1,x2) Input State(x1,x2)   00 01 10 11 00 01 10   ① ① ① 1 0 0 - -   ② 1 3 - 1 - - -   2 ③ ③ ③ ③ - 1 1</td></t<> | Input State(x1,x2) Input State(x1,x2)   00 01 10 11 00 01 10   ① ① ① 1 0 0 - -   ② 1 3 - 1 - - -   2 ③ ③ ③ ③ - 1 1 |

### PART B

### Answer any two full questions, each carries 15 marks.

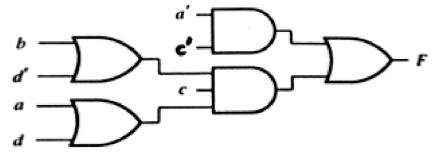

4 a) Find all of the static hazards in the following network. For each hazard, specify (7.5)the values of the variables which are constant and the variable which are changing. Indicate how all of these hazards could be eliminated by adding gates to the existing networks.

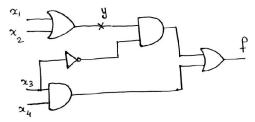

b) For the given circuit, find the tests to detect the faults  $x_3$  S-A-0,  $x_3$  S-A-1, yS-A-0 (7.5) and yS-A-1.

5 a) Explain Essential hazards in asynchronous sequential networks. What are the (7.5)constraints to be satisfied to avoid Essential hazards? (7.5)

(3.5)

(4)

(10)

- b) Explain Kohavi algorithm.

- a) Differentiate positive skew and negative skew. 6

- b) Explain Jitter. What causes Jitter?

- c) Explain different test pattern generation for BIST. (7.5)

# PART C

#### Answer any two full questions, each carries 20 marks.

7 a) Explain different kinds of PLA folding.

Page 2 of 3

# F

# F7196

|   | b) | Draw and explain the architecture of Xilinx 9500-family CPLDs. Also explain the | (10) |

|---|----|---------------------------------------------------------------------------------|------|

|   |    | function block architecture.                                                    |      |

| 8 | a) | Describe the different test generation techniques for PLA.                      | (10) |

|   | b) | Explain the internal structure of an XC4000-series CLB.                         | (10) |

| 9 | a) | Explain different testable PLA Designs.                                         | (10) |

|   | b) | Using suitable illustrations explain the XC4000 programmable interconnect.      | (10) |

|   |    | ****                                                                            |      |